- 06 June 2013

- Kristof Beets

In the previous three sections, I discussed the need to match market requirements, our rapid adoption of multiple graphics APIs, and our uncompromising support for GPU compute across all our PowerVR GPU cores.

In this section, I will dive more deeply into the underlying hardware architecture, highlighting a selection of the patented unique features, as well as the flexibility of our modern efficiency-focussed GPU architecture, which made it possible to support today’s requirements on our Series5XT architecture.

Mobile graphics are all about efficiency

Imagination’s PowerVR GPUs have always been different: from day one, our hardware architects realised that brute force solutions will sooner rather than later run into problems, and with mobile GPUs these problems all too easily include power consumption and/or bandwidth limitations.

By focussing our whole architectural design around ‘efficiency’, we are guaranteed to always come out ahead of our competition – be it better performance versus power consumption, or, equally important, better performance versus an always limited bandwidth budget.

This efficiency focus made it easy for us to target the mobile market in 2001, as in this market power consumption is critical. Battery capacity is always limited – linked to this, heat is also increasingly a problem due to the rise in popularity of the thin form factor.

But equally important, bandwidth in mobile is limited, as for power reasons the memory infrastructure is unified and shared, and hence equally restricted.

PowerVR is the only Tile Based Deferred Rendering (TBDR) implementation

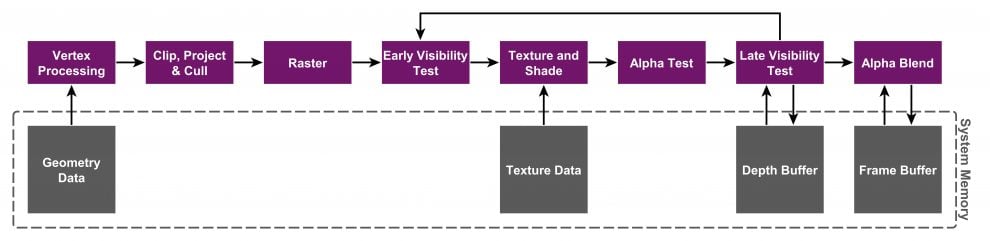

Driven by our focus on efficiency, our architects rejected the brute force Immediate Mode Rendering (IMR) approach early on, as it’s extremely wasteful in bandwidth usage and processing efficiency as illustrated below:

The Immediate Mode Rendering (IMR) graphics pipeline

The Immediate Mode Rendering (IMR) graphics pipeline

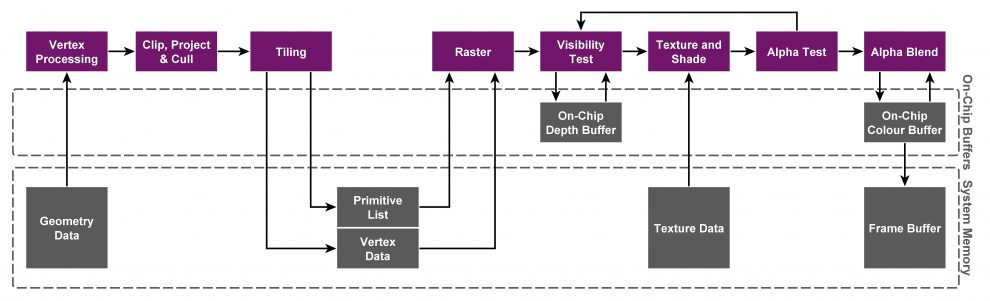

We considered Tile Based Rendering (TBR) which ensures 100% cache efficiency for depth buffers and colour buffers (thus restricting a lot of bandwidth to be only on-chip – a significant efficiency gain), but equally found that this approach still resulted in lots of wasted cycles and bandwidth on texturing/shading of invisible pixels as illustrated below:

The Tile Based Rendering (TBR) graphics pipeline

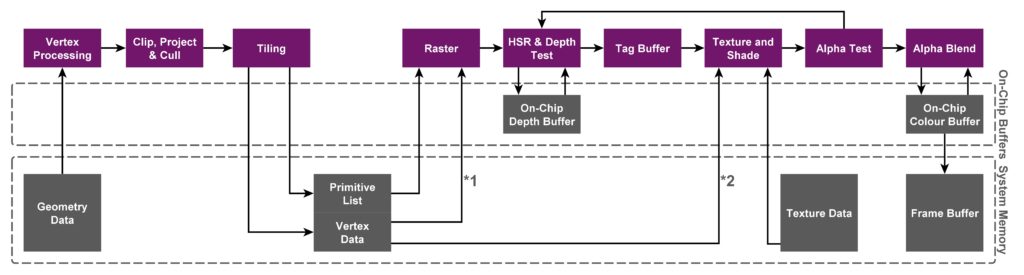

So ultimately our architects designed what is today known as true Tile Based Deferred Rendering (TBDR), a rendering approach which aims to ‘delay’ or ‘defer’ all texturing and shading operations until their visibility is known. This is illustrated below:

The Tile Based Deferred Rendering (TBDR) graphics pipeline

By now, you’re probably wondering why I feel the need to add the term ‘true’ to my reference of TBDR. The reason for this is simple: competitor marketing hype machines have been trying to redefine what we have been calling TBDR for the past 20 years.

Their reasoning is that TBR ‘defers’ the processing of pixels until after the geometry has been tiled, and hence they feel the need to claim that ‘TBR’ = ‘TBDR’. Unfortunately, this ignores our 20 year standing definition of ‘true’ TBDR, where the ‘deferring’ is about deferring the texturing/shading processing. Basically, make sure that when you see a claim that a GPU has TBDR, it’s actually really the ‘true’ TBDR.

To date, TBDR continues to be the most advanced and efficient approach to rendering. Over time, ‘brute force’ solutions have adopted an ever-increasing number of TBDR properties from tiled rasterisation, to tiled rendering approaches for efficient usage of eDRAM, to software assisted ‘Deferred Rendering,’ where depth pre-passes are submitted by the application to try and approximate the inherent benefits of the hardware based ‘deferred rendering’ of our PowerVR TBDR architecture.

Our efficiency through TBDR ensures the lowest possible bandwidth usage and the lowest amount of processing cycles per frame, and all of this leads to high performance efficiency and the lowest power consumption per frame.

In the next blog post, I will continue to discuss how PowerVR SGX puts efficiency first through a series of unique architectural features like multithreading and multitasking that allow Series5XT cores to deliver uncompromising performance while keeping power consumption at a minimum.

If you have any questions or feedback about Imagination’s graphics IP, please use the comments box below. To keep up to date with the latest developments on PowerVR, follow us on Twitter (@ImaginationTech) and subscribe to our blog feed.

‘Understanding PowerVR’ is an on-going, multi-part series of blog posts from Kristof Beets, Imagination’s Senior Business Development Manager for PowerVR. These articles not only focus on the features that make PowerVR GPUs great, but also provide a detailed look at graphics hardware architectures and software ecosystems in mobile markets.