- 01 February 2022

- Robert Owen

Take a look through the academic materials now available about RISC-V. You will find a wealth of information about SoC creation, inventing special instructions, security, and numerous implementation enhancements. But what about the vital “Start Here” materials – the foundation needed by teachers to bring the fundamentals of computer architecture to life?

RVfpga contains the relatively unglamorous beginnings of the education process. Every computer science, computer engineering, and electronic engineering student needs a solid foundation in computer architecture. It’s an area that touches more fresh minds than almost any other technical subject, yet many university course curricula in this area offer content that is often years old, and therefore outdated. Even more concerning is that it is usually based on a simplified core or an obfuscated; (encrypted) “black box”.

One example of such material says that “Labs are based on a simple 5-stage processor for education purposes”. Surely we owe it to our students to teach real-world solutions? It may be slightly harder, but using real-world implementations programmed by industry-standard software development tools is a much better way to set up our future graduates for success in their careers. Put simply, why have “a simplified core” when you can have a real one? In the same spirit, why use restricted “free version” development tools when you can use industrially-proven tools?

This is the fundamental principle that underpins the Imagination approach to our university courses.

Based on real-world designs

RVfpga enables students to understand computer architecture through hands-on experience with the RISC-V architecture and its ecosystem. Yes, the theory is all there too, but RVfpga brings those diagrams to life through excellent hands-on labs.

The materials are free of charge, on request from Imagination, and use an open-source core from Western Digital, which can be run in a simulator or on a Digilent Nexys A7 FPGA board. This core is real-world: it’s fully verified, already in silicon, and is used by Imagination as the firmware processor inside its latest GPUs (IMG A, B, and C-Series) and by Western Digital in data storage systems.

Many universities already have the Digilent Nexys A7 or Nexys 4 DDR hardware, and future extensions of the RVfpga course will include other lower-cost hardware, as well as introducing a virtual version of the Nexys A7 for online courses. The programming tool is PlatformIO, a widely known and popular RISC-V integrated development environment.

RVfpga system uses Chips Alliance’s SweRVolf SoC, based on Western Digital’s RISC-V SweRV EH1 core. The SweRV is a fully-verified production-level processor core that is completely open-source.

It is at the centre of a vibrant, expanding ecosystem with many useful open-source and commercial tools available, including simulators, models, integrated development environments, virtual hardware, and pre-configured FPGA-ready SoC implementations.

The RVfpga RISC-V Brochure materials are extensive, including a detailed set-up guide for the teachers, a student manual, and lecture slides. There is enough material for two semesters. Furthermore, the follow-on course RVfpga-SoC takes the students into SoC design and shows them how to build an SoC, run the Zephyr RTOS, and program the core using TensorFlow Lite. In total, there are high-quality proven materials to last up to three semesters. We believe this is the largest collection of useful teaching materials on this subject.

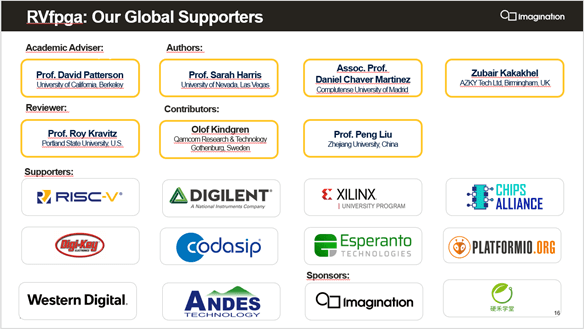

Content created by experts

We have a strong belief that the best teaching materials must be written by teachers who are experts in the subject. Professor Sarah Harris of UNLV (Las Vegas) and Associate Professor Daniel Chaver-Martinez of UCM (Madrid) are the principal authors, along with contributions from Zubair Kakakhel and M. Hamza Liaqat (AZKY Ltd, UK). Our reviewers and guides are Professor David Patterson of UC Berkley, Professor Roy Kravitz of Portland State University, and Professor Liu Peng of Zhejiang University.

The first Lab is about getting the RVfpga system on the FPGA, and then how to write assembler and C programs that run on the core. By Lab 11, students are studying the microarchitecture and then investigating the pipeline stages using performance counters and looking at memory instructions. Later Labs look at custom instructions, instruction cache, and data memories.

We will soon have a virtual version of the Nexys A7 board, called “ViDBo”. This will enable self-study massive open online courses (MOOCs) in both English and Chinese, enabling students worldwide to benefit from these materials independently. We are also seeing growing demand from start-up companies and inventors to use these materials. MOOCs will be a very convenient entry point for them. Furthermore, we want to take these materials “on the road” through a series of “Teach the Teacher” workshops in major RISC-V markets worldwide.

Since the launch of the first ten Labs in November 2020, more than 1,000 Universities and individuals have requested and downloaded RVfpga. In November 2021 we released v2.0 which added Labs 11 to 20. The regular requests for these expanded materials, the strong attendance at webinars, and the thriving RVfpga Forum demonstrate a strong appreciation of the value of the materials. It is our wish that these materials become the foundation level of computer architecture in undergraduate education: a solid and powerful base from which to grow young minds into innovators using the springboard that RISC-V brings.

Exciting times

Why did Imagination make its first RISC-V “product” a product for education? We saw a unique opportunity. We had pioneered the soft-core-on-FPGA approach with MIPSfpga and had an expert team ready to run. Imagination had adopted RISC-V for internal use and was considering its entry into RISC-V-based CPU design. RVfpga has enabled Imagination to put something valuable into the RISC-V ecosystem, demonstrating that it is a generous team player showing respect for the open-source community. It has also enabled us to build our reputation in RISC-V from education upwards – a complete reversal of the usual approach.

Since RVfpga was launched, we have subsequently announced we are designing RISC-V CPUs from scratch called “Catapult” and have begun to offer IP and development tools.

These are exciting times for our industry and a once-in-a-generation inflection point in the approach to CPUs. We believe in sharing real-world, in-silicon solutions with students. So, as we said above, why use a “simplified education core” when you can use genuine cores, used in current real-world designs. Thanks to this, and the quality of its materials, our RVfpga: Understanding Computer Architecture course will ensure that graduates in our industry will be fully equipped to take advantage of the liberating design freedoms of this new world.

- Register here for the Imagination University Programme (“IUP”)

- Request course materials