- 20 April 2012

- Benjamin Anuworakarn

We are now back from various shows around the world where we had lots of discussion with developers about the use and longevity of Imagination’s Tile Based Deferred Rendering-based (TBDR) PowerVR architecture. Some had never heard of it (mainly those who were moving down from the console and PC space) and others who wanted to know if TBDR would ever run out of steam. To that end, we are just setting out the whys and wherefores’ of TBDR to help people’s understanding. If you’re reading this, the chances are you know what Imagination PowerVR is, for those of you who don’t, it’s the mobile GPU architecture found in the majority of all mobile and embedded devices.

If you do, you already know that PowerVR likes to, as we say in the office, “render funny”. Unlike the graphics card in your desktop computer, PowerVR is not an Immediate Mode Renderer (IMR); it is a Tile Based Deferred Renderer (TBDR). Today, we want to explain to you what that means and answer the rather intriguing question of “why?”

What is TBDR?

The question “What is TBDR?” has two different answers, one long, one short, here I hope to furnish you with the short answer.

PowerVR graphics: The Tiling Bit

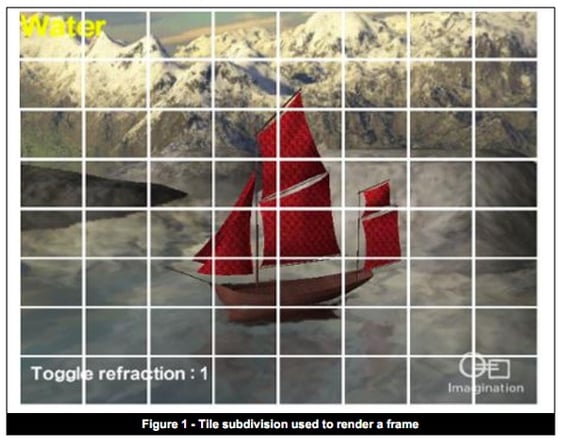

Tiling really is as simple as it sounds. On a basic level, the framebuffer is split into little tiles, of a fixed size, with each tile being drawn individually once an entire scene has been submitted; all the vertex information for a scene is gathered, clipped, projected, culled, and transformed, before being placed into a small container in memory stating which triangle is in which tile. Once the vertex processing is done, fragment processing is performed, but because the location of every triangle is known ahead of time the chip can make what I like to call “informed decisions”.

Informed Decisions or ‘The Deferred Bit’

Obviously any GPU that performs tiling must defer in a sense, but when we at PowerVR talk about ‘Deferring’ we mean something a little different. To us, the “Deferred” step refers to those “informed decisions” I mentioned just a moment ago; what, in technical parlance, is called “Hidden Surface Removal” (HSR).

We should first define one of the great bugbears of modern graphics, “Overdraw”. “Overdraw” is what happens when you draw into a pixel more than once, because you’ve wasted time processing one fragment when it’s going to overwritten by another fragment closer to the camera.

Clearly this is a bad thing, and that’s where those “informed decisions” come in; by knowing ahead of time exactly what fragments of what triangles are going to contribute to the final framebuffer we can safely ignore those that won’t. This process of discarding unrequired fragments is the aforementioned “Hidden Surface Removal” and is a major feature, as you will hopefully understand very soon.

Yes, but…Why?

Whenever you design a new technology it’s important to consider the requirements for that technology. In the case of mobile and embedded systems it’s always been about the big three, power consumption, die size, and performance. You can always make a chip smaller simply by stripping out performance, or letting “Moore’s Law” do the work for you, and save power to boost, but you can do more than that; you can design your technology from the ground up with these things in mind…and that’s where TBDR comes in.

The first of the stages I mentioned previous, “Tiling”, allows the chip to keep an entire section of the framebuffer on chip until it’s completed. If the tile never leaves the chip, then once it’s loaded in, the only system bandwidth you’re going to consume is during texture reads in your fragment shaders. All this saved bandwidth means less power is consumed for each frame, and thanks to clever optimizations on our end your applications performance goes up too.

The second of these stages, the “Deferred” stage, means that the chip doesn’t waste time processing fragments that no-one is ever going to see. These are thrown away. While this saves power, and delivers better performance all on its own, it also saves even more bandwidth; after all, every fragment you’re not processing is a bunch of textures you’re not having to read, which saves even more bandwidth, and even more power, and delivers even better performance.

At the end of the day, Imagination PowerVR does TBDR because we believe it is, fundamentally, a better architecture. “Tiling” and “Deferring” save memory bandwidth, improve performance, and save power, and that’s why it’s so widely adopted in power restricted environments like the mobile and embedded markets.

Our motto for TBDR is ‘Work Smarter, And Harder’

If you want to know more about our technology and products or to simply download the SDK and get working on our Imagination PowerVR graphics family, they're available on our Imagination developer website.